PDNExpert

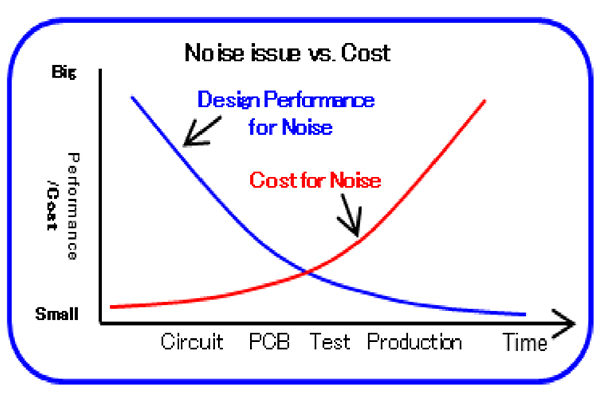

In recent years issues caused by unexpected power bus noise have increased and it is becoming more difficult to design PCB without operational failure. PDNExpert can be utilized at the early design stage and effectively reduce power bus noise by taking into account the board, capacitors, chip and package.

Benefit of Pre-PI Noise Analysis

- 1.Reduce design cost

- - The best constraints in early design stage, Board Outline, Plane Shape, Stackup, Location of Chip, Capacitor

- 2.Reduce iteration cost

- - Hiding PI issue correction in the early design stage. IR drop, Dynamic IR drop, EMI (Radiated noise from Plane)

- 3.Reduce TAT(Keeping delivery)

- - Minimize PI-issue before the verification stage.

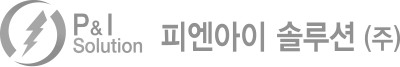

Early Design Stage PI Optimization = Cost Reduction

PDNExpert can be used at pre-layout stage to optimize capacitors taking into account capacitance, quantity, stack-up, and location on the board without layout data. PDNExpert allows you to optimize Power Integrity by analyzing stack up, plane shape and component placement.

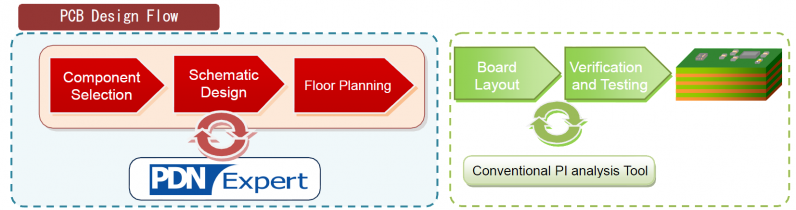

Create Complex Power Plane and Place Capacitors

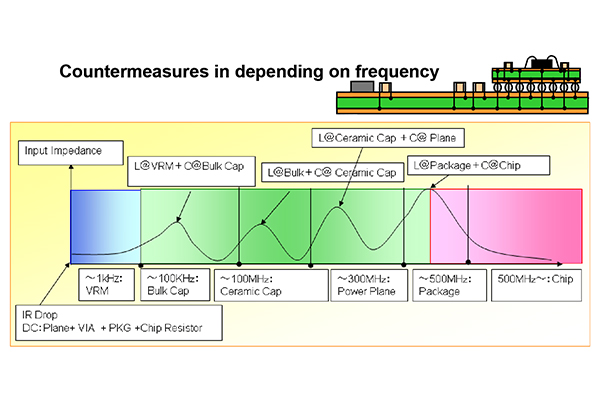

Use capacitor optimization features to see how many and what kind of capacitors you need to meet your target impedance. You can then create complex plane shapes and place capacitors on the board to see how you can reduce input impedance.

Chip/PKG/PCB Total Analysis

Taking into account effects of chip/PKG is critical for performing accurate power integrity analysis. It is due to the significance of the effects of anti-resonance between PCB and chip/PKG and specifying the frequency range where chip/PKG characteristics are dominant as signal speed increases. PDNExpert can take these things into account at an early design stage and enable optimal chip selection.